Electrical Engineering > QUESTIONS & ANSWERS > Digital Integrated Circuits University of WaterlooECE 637Solution_Adder (All)

Digital Integrated Circuits University of WaterlooECE 637Solution_Adder

Document Content and Description Below

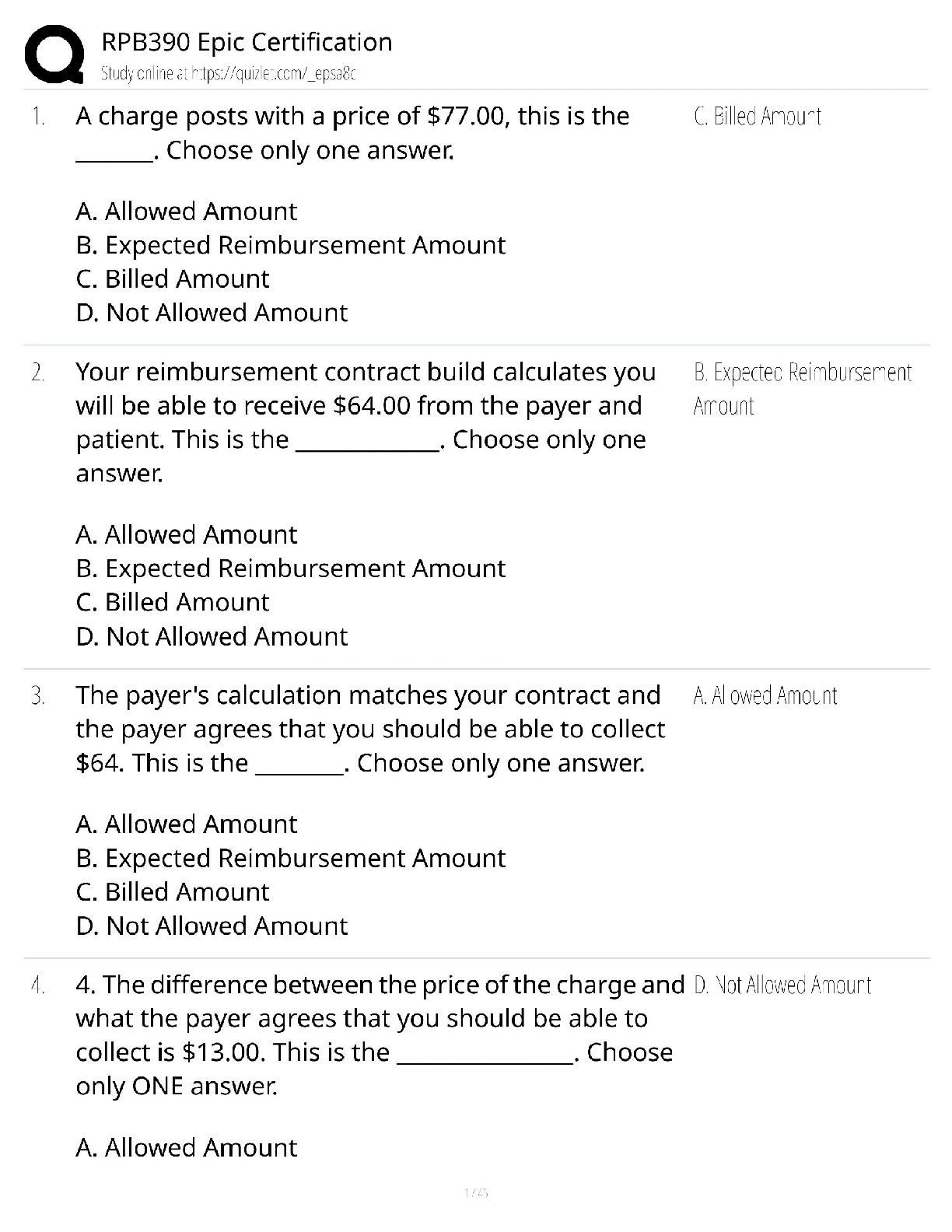

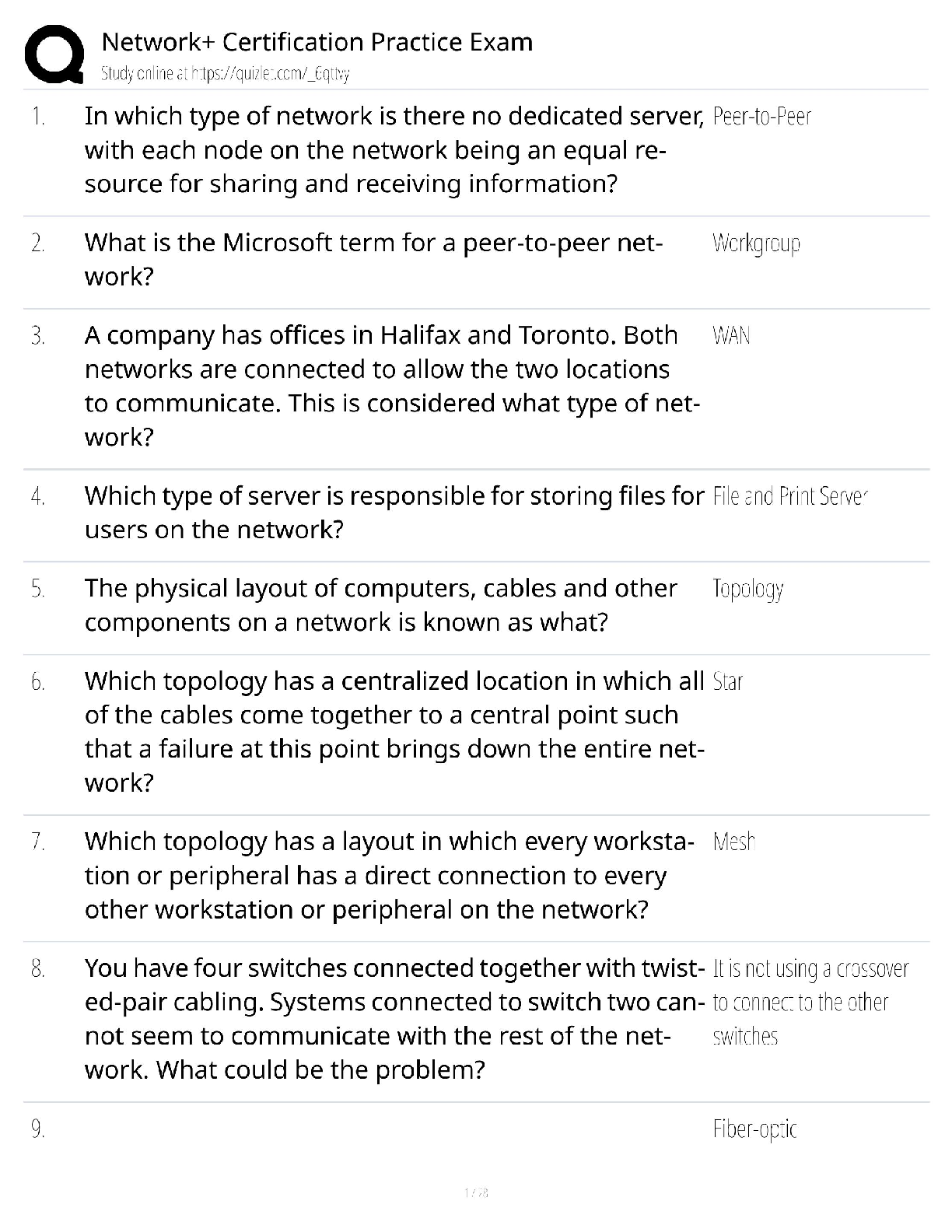

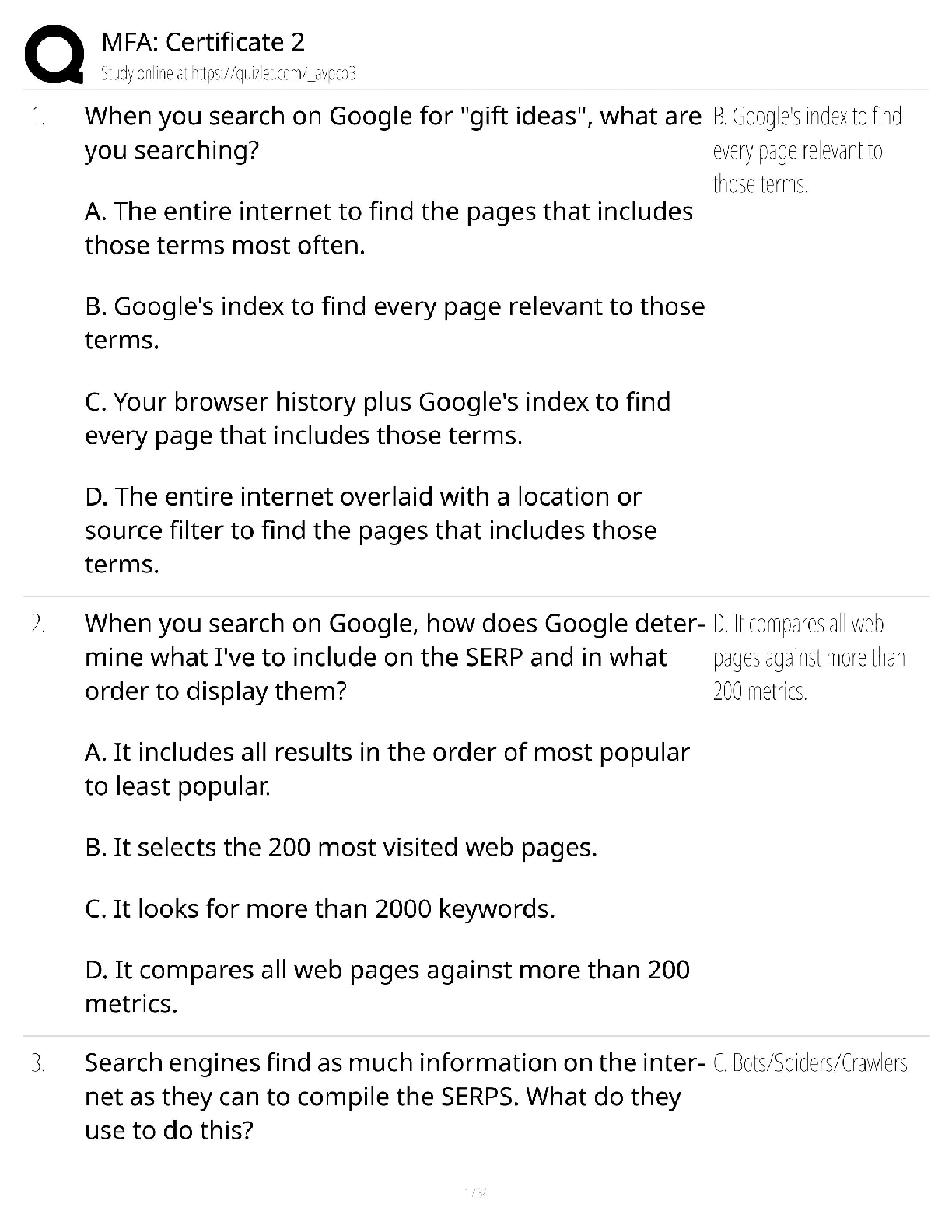

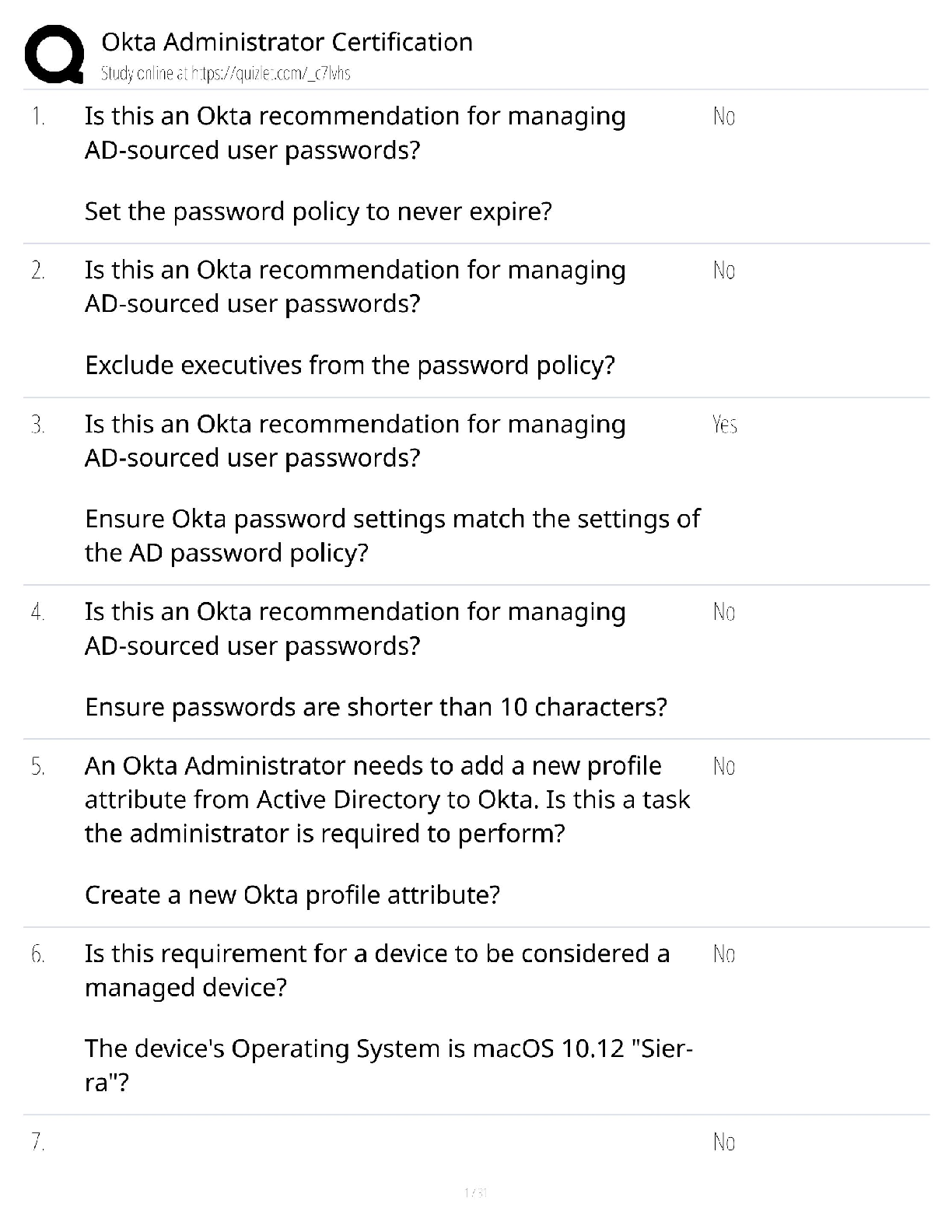

ECE-637, Assignment #1 Chapter 11, Digital Integrated Circuits, a Design Perspective, J. Rabaey, 2nd Edition 11.2) A magnitude comparator for unsigned numbers can be constructed using full adders a ... nd Boolean logic gates as building blocks. For this problem you are given a cell library consisting of full adders and arbitrary fan-in logic gates (i.e., AND, OR, INVERTER, etc.). a. Design an N-bit magnitude comparator with outputs A B and A = B using a minimal number of Boolean logic gates. The result of this process should be a diagram in the spirit of Figure 11.5. Specify the value of any required control signals (e.g., Cin ). A=B if A-B = 0 A-B = A+ B +1 [Show More]

Last updated: 3 years ago

Preview 1 out of 6 pages

Buy this document to get the full access instantly

Instant Download Access after purchase

Buy NowInstant download

We Accept:

Reviews( 0 )

$6.00

Can't find what you want? Try our AI powered Search

Document information

Connected school, study & course

About the document

Uploaded On

Apr 28, 2021

Number of pages

6

Written in

All

Additional information

This document has been written for:

Uploaded

Apr 28, 2021

Downloads

0

Views

71

.png)

.png)

.png)

.png)

.png)