1007ICT LOGISIM ASSIGNMENT

1007ICT: Computer Systems and Networks

Logisim Assignment

Circuit Function:

3-8 decoder

To start the circuit that this task requires, we firstly need to have 3 input lines for both variabl

...

1007ICT LOGISIM ASSIGNMENT

1007ICT: Computer Systems and Networks

Logisim Assignment

Circuit Function:

3-8 decoder

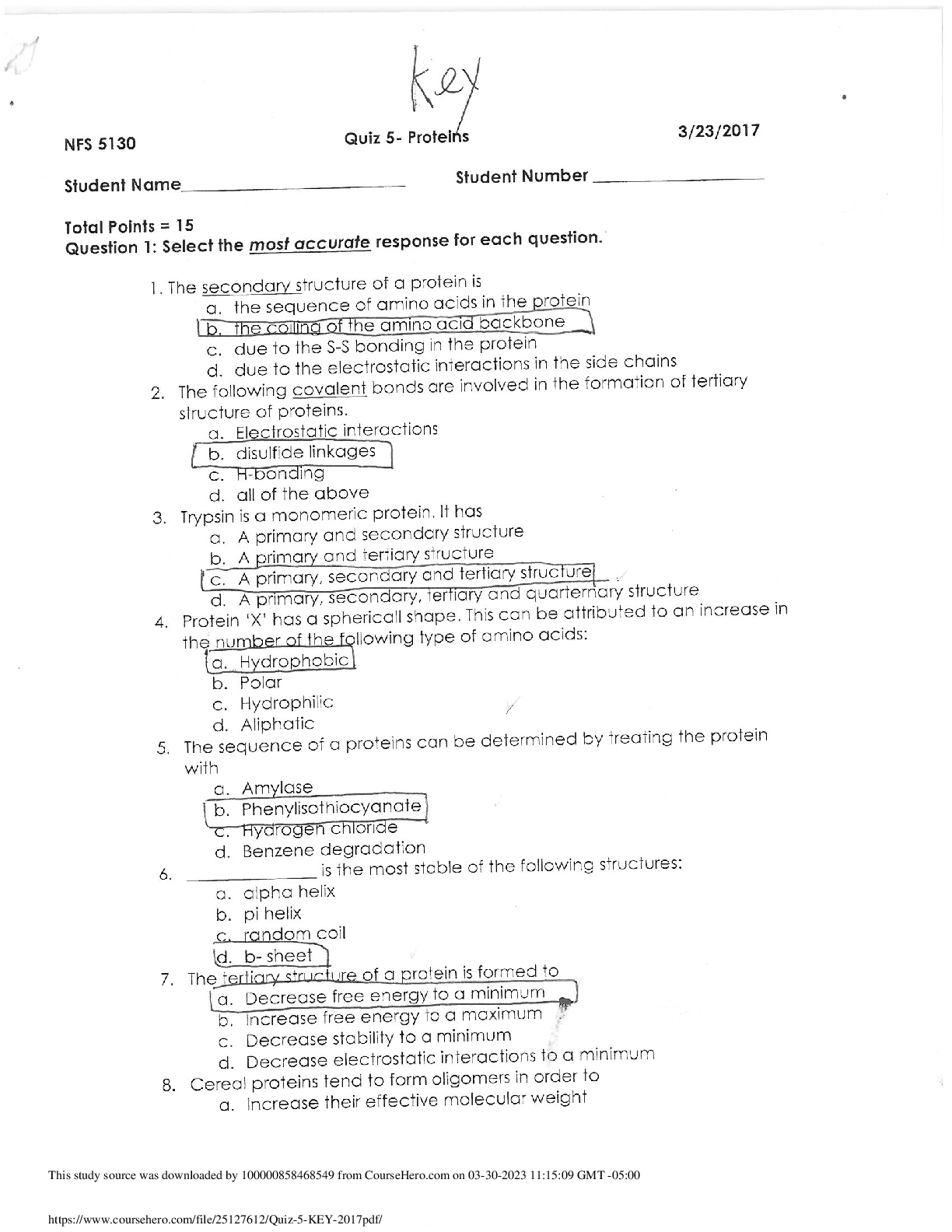

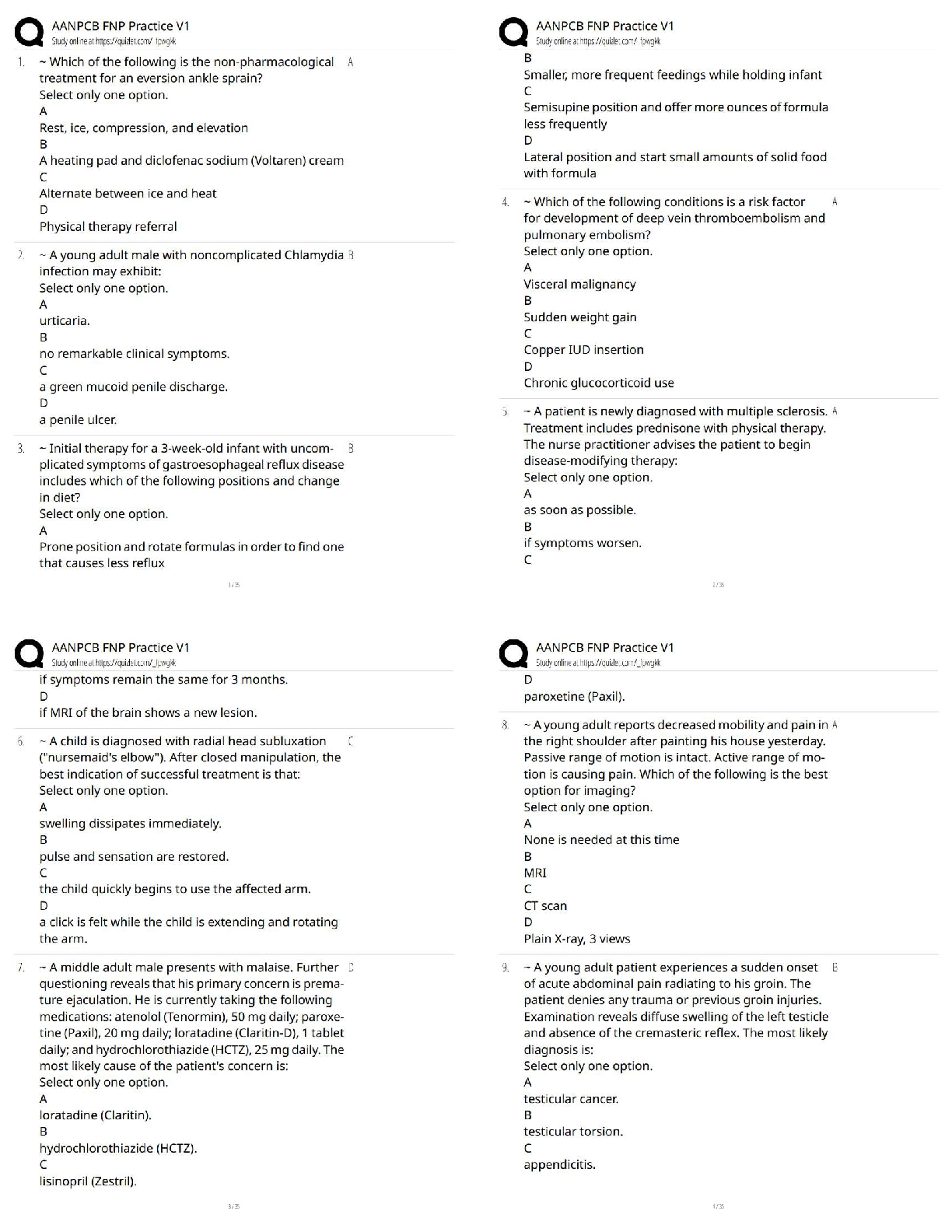

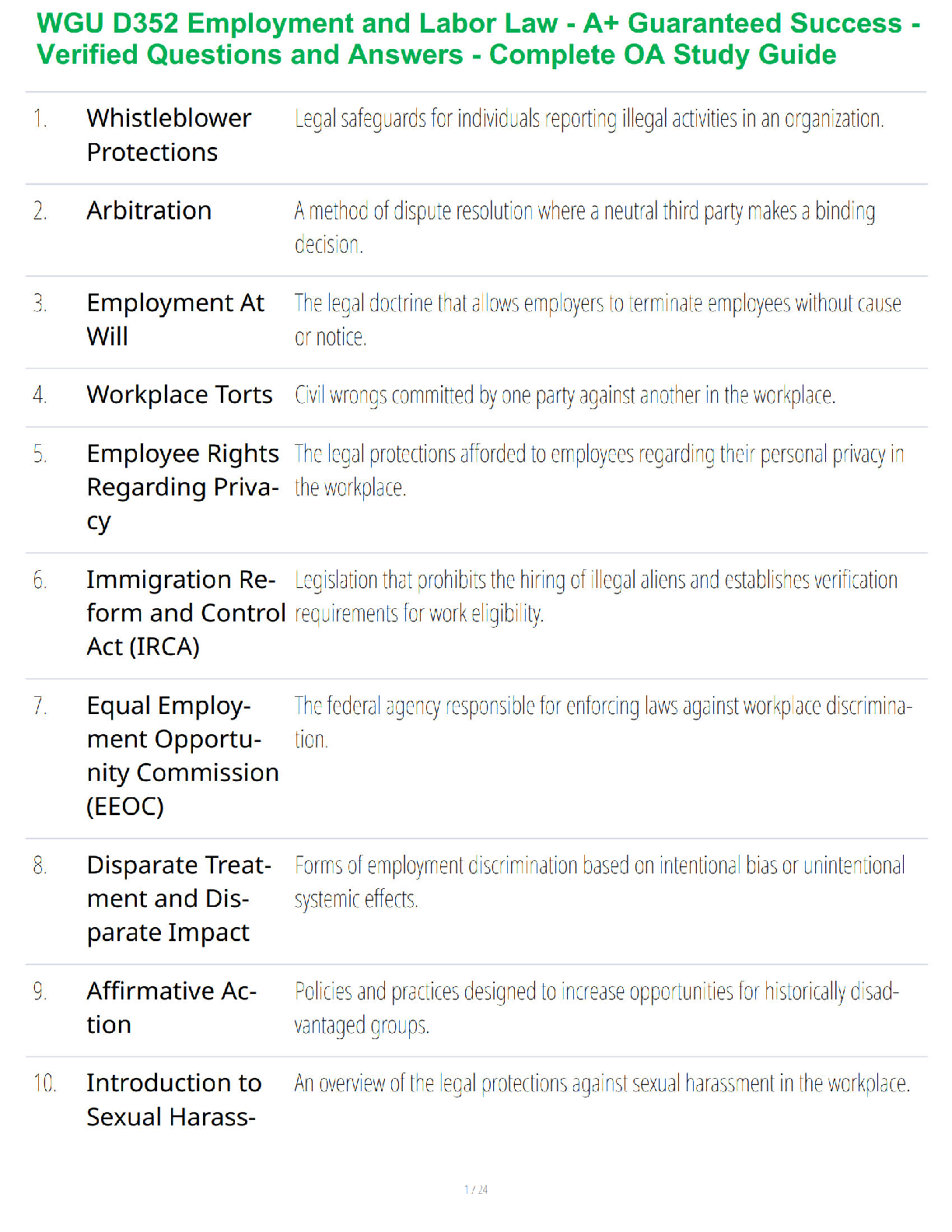

To start the circuit that this task requires, we firstly need to have 3 input lines for both variables

(velocity and acceleration) respectively. Therefore, as we have 8 different values (0-7) for both our

velocity and acceleration, we must use a 3-8 decoder as per Figure 1. (Note that Figure 1 represents

the circuit for both velocity and acceleration due to both variables having same values). The reason

why this decoder is required is due to our inputs starting in binary form where the aim is to

represent this value in a single output line. For example, the binary value for 6 is 110; in order to

represent this value in just one output line, the 3-8 decoder is applied. Consequently, this leaves 8

output lines (0-7) for both the velocity and acceleration decoders, hence, we are expecting 64

different outcomes.

V0 to V7 selectors

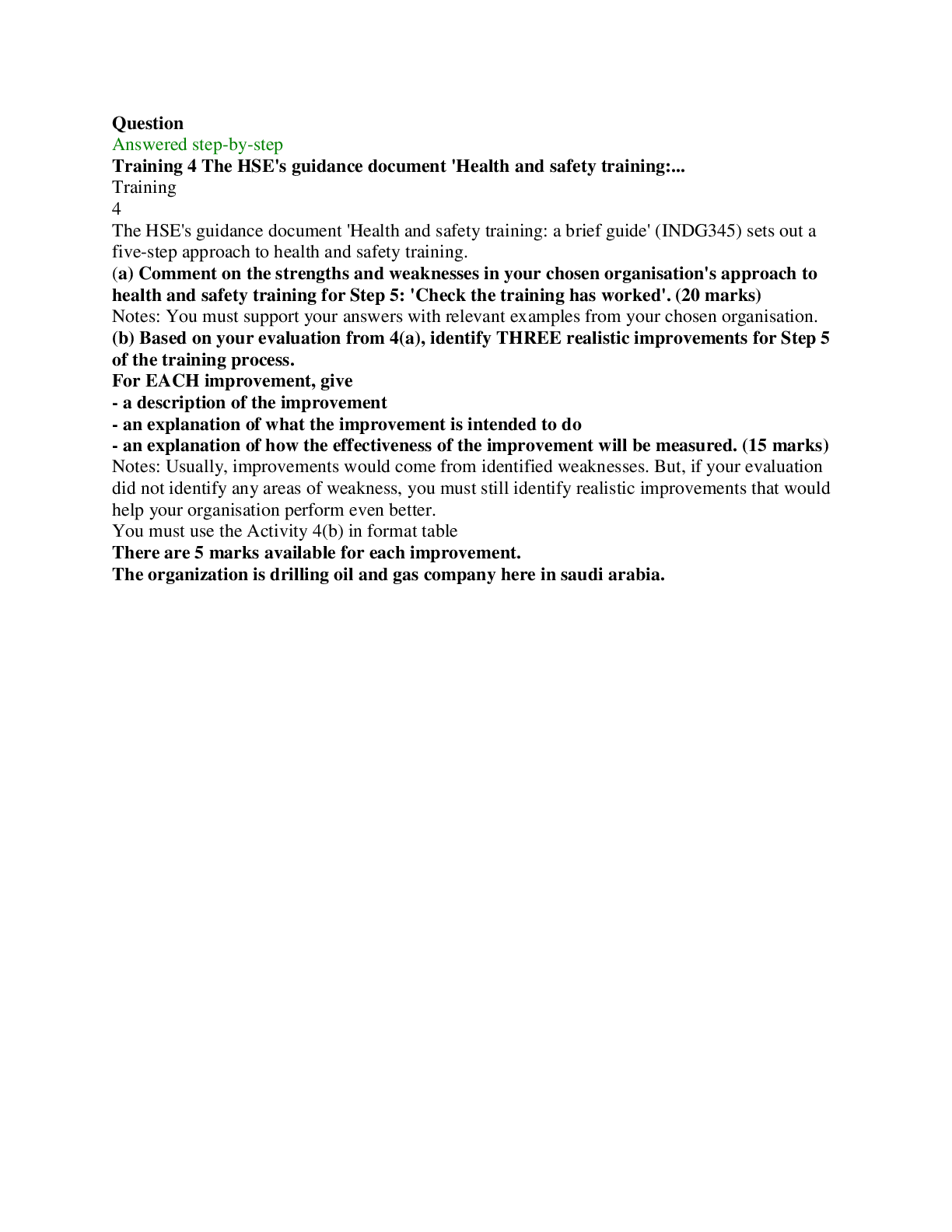

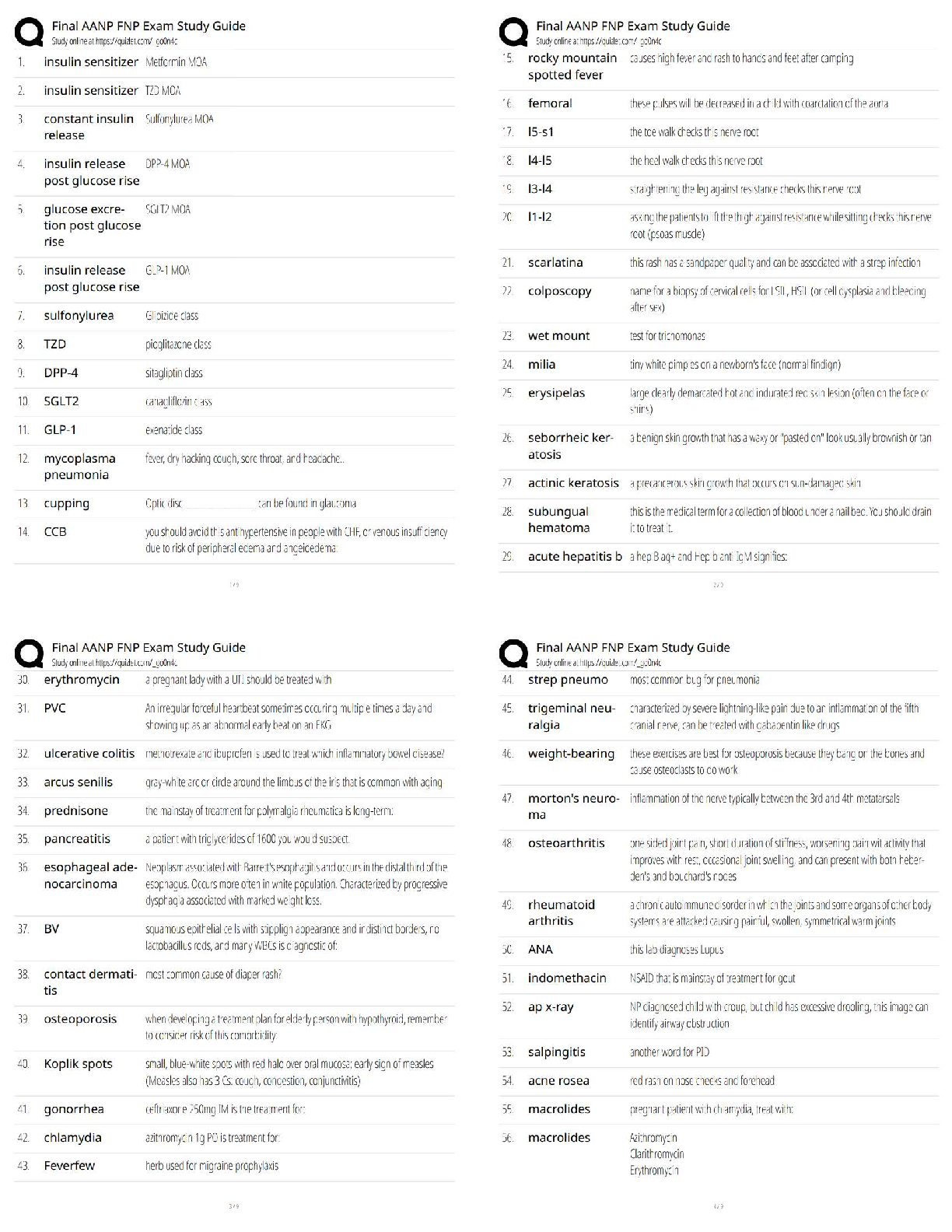

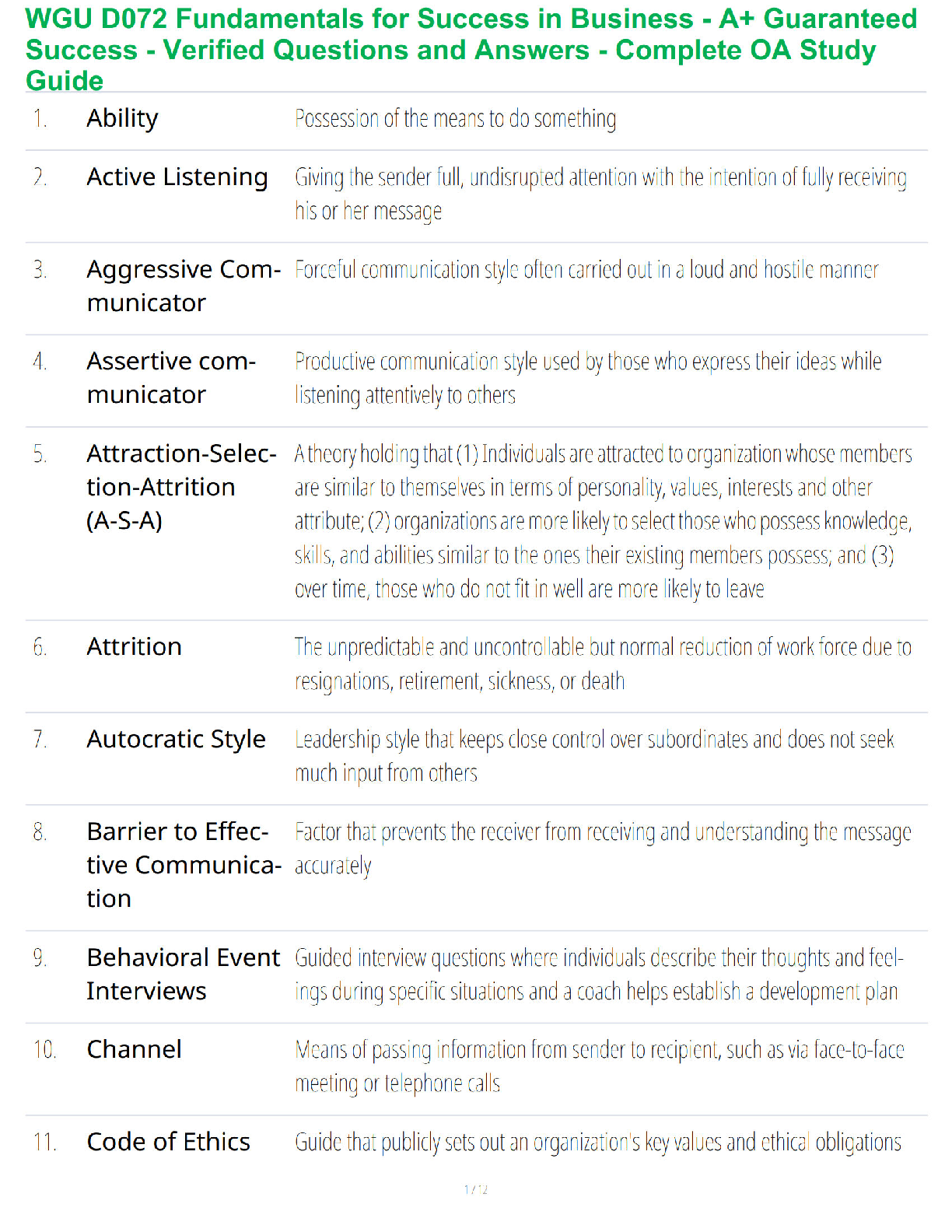

In the scenario presented by Figure 2, the implementation of 8 different selectors were applied. The

labels of these selectors range from V0 to V7. This was purposefully done to show that each box only

represents one velocity value with the remaining 8 values for the acceleration. The only problem that

occurs is that all acceleration values are linked together and causes all these lines to be activated

once its specific value is selected. (e.g. when we select an acceleration value of 5, all sub circuits from

V0 to V7 have that value activated). Consequently, 8 different selectors with different layouts were

constructed in order to counter any discrepancies.

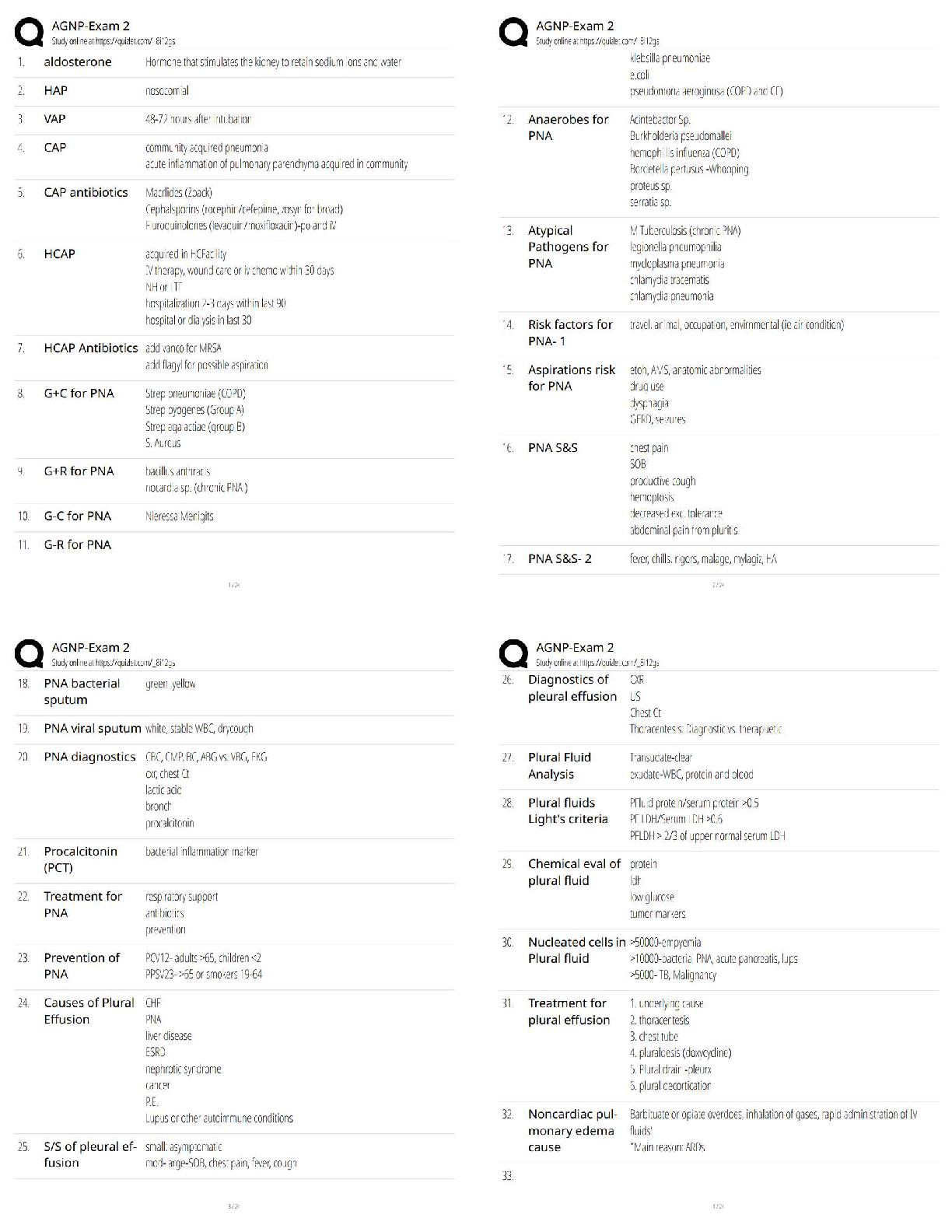

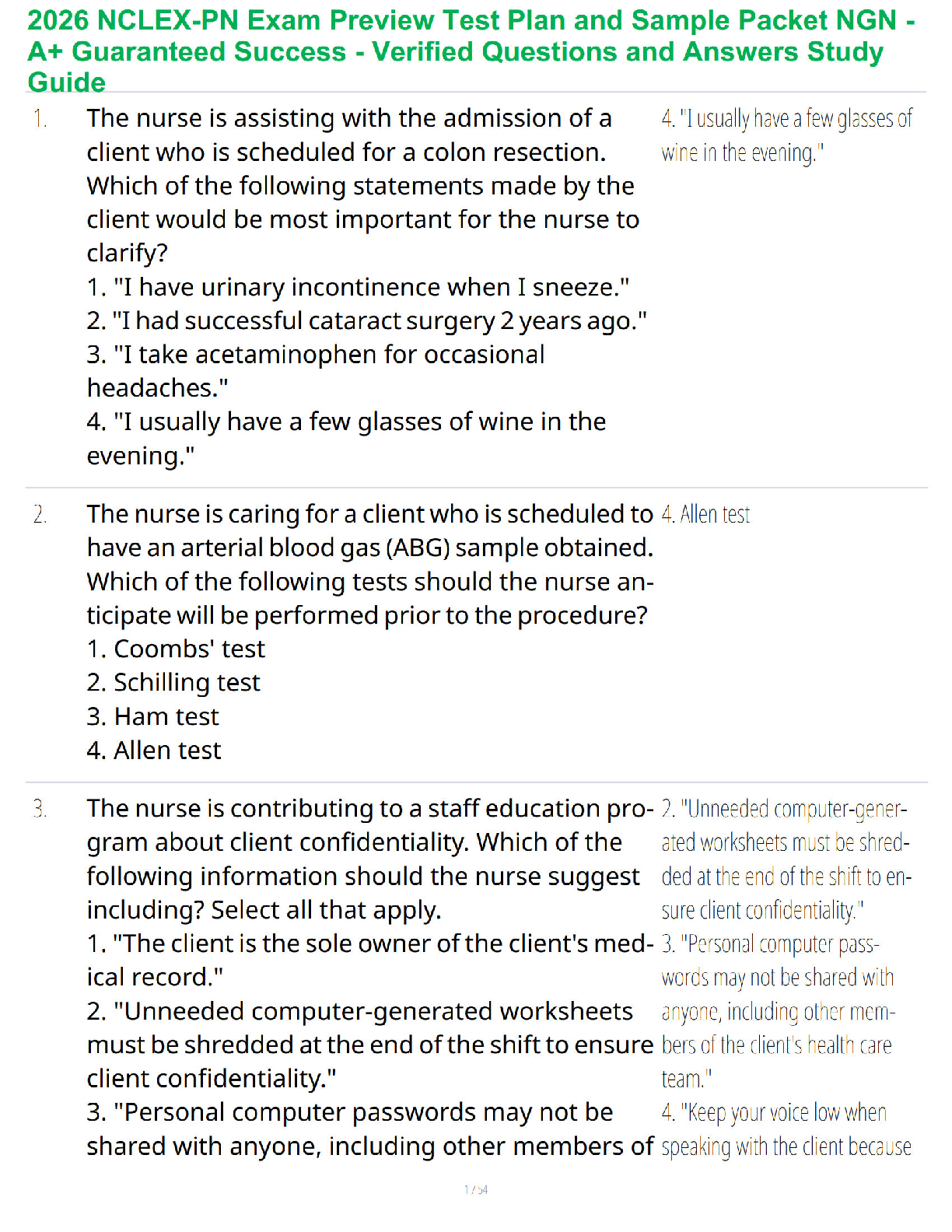

Final Part A layout (Sub circuits)

As seen in Figure 3, the two above circuits have been made into sub circuits to keep the visual display

reasonable. After the V0 to V7 selectors have produced an output, the wires then present another

selector like layout that eventually tells the user if the acceleration is successful or not.

Final Part B layout (Sub circuits)

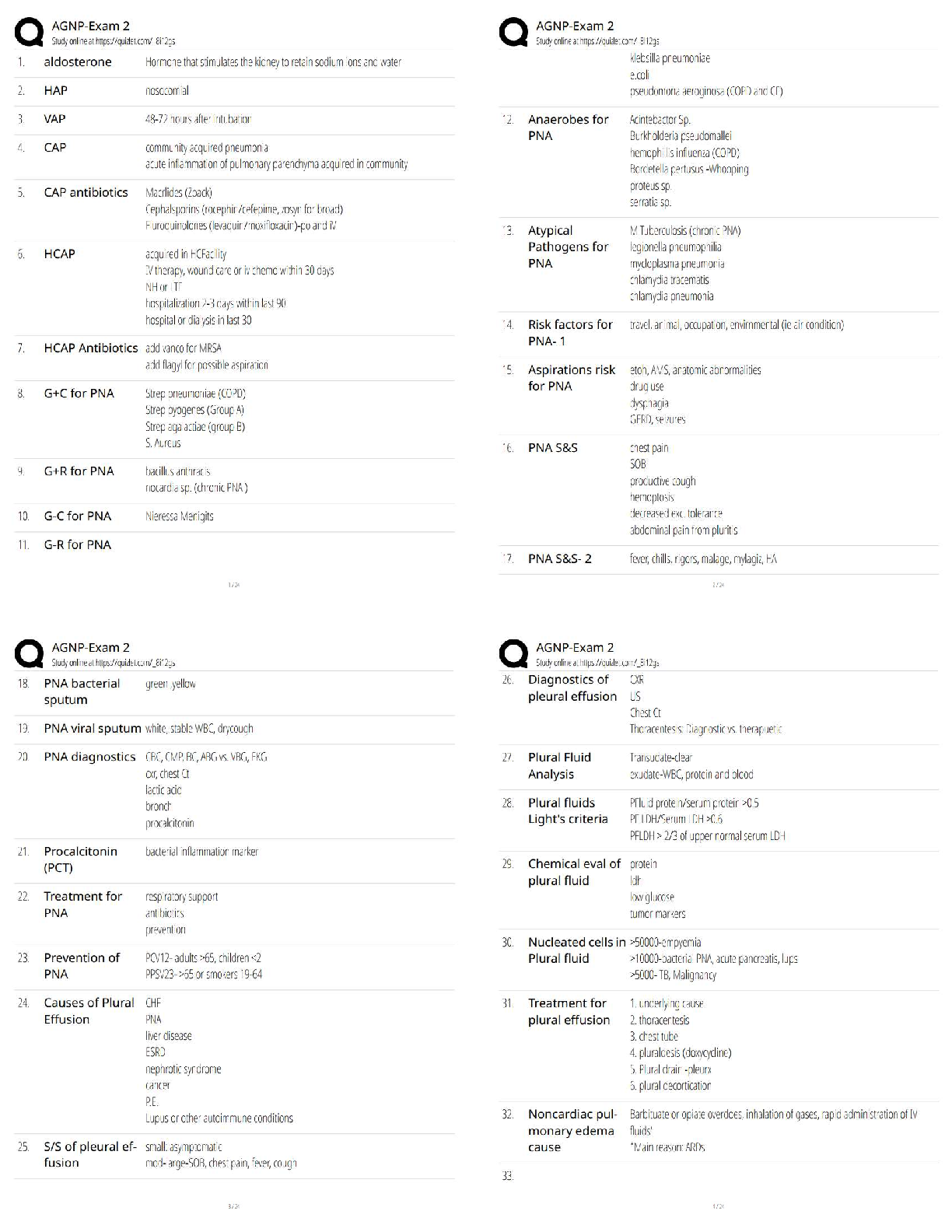

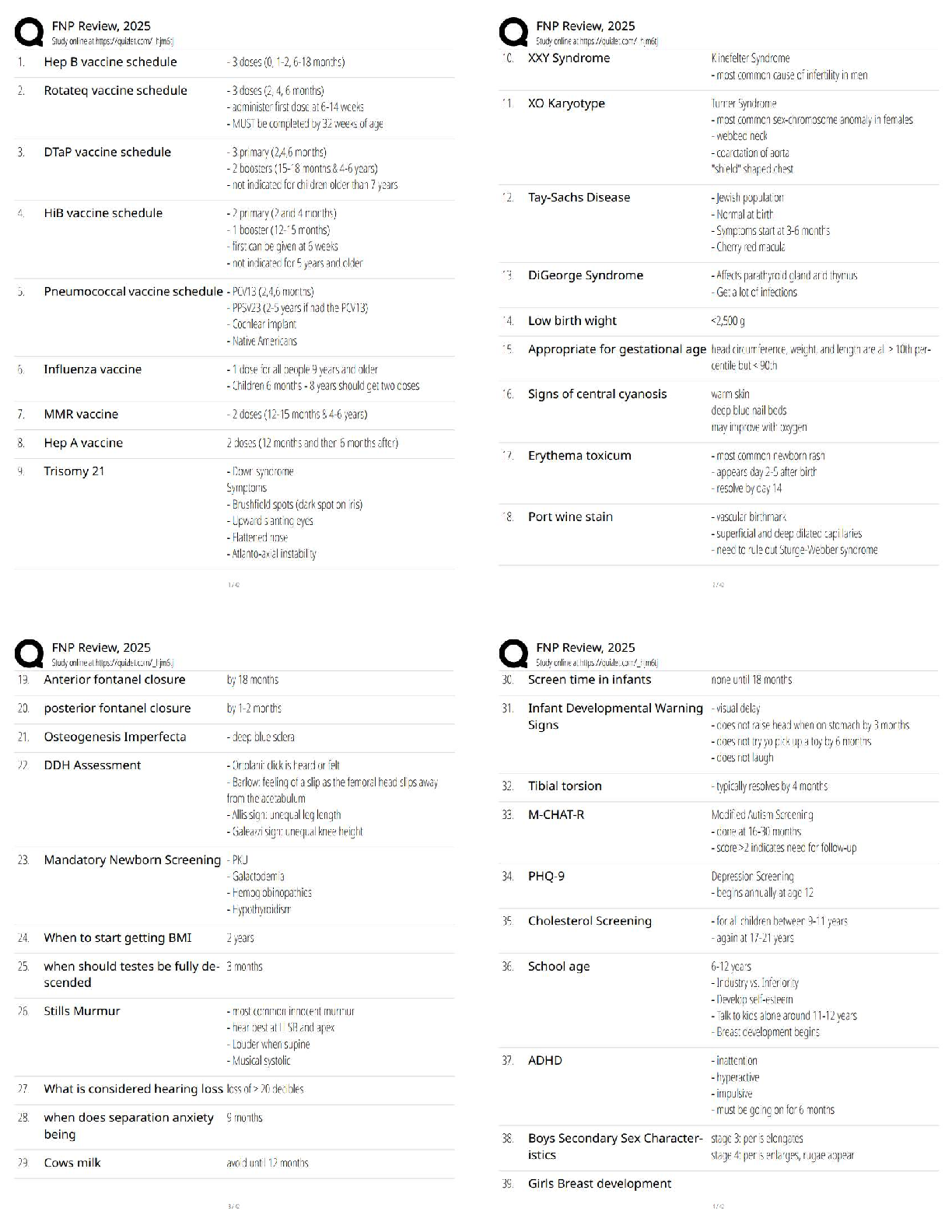

Figure 4 represents part B of this task where we are asked to provide additional circuitry that keeps

track of how many successful and unsuccessful accelerations are presented. Firstly, the part A circuit

was made into a sub circuit which releases an output of successful or unsuccessful. Based on the

result from the part A circuit, the successful or unsuccessful counters will be activated. These

counters are connected to a button to allow for no additional counting when changing different input

values. The ‘Q’ output of both outcomes then goes into a comparator, which determines whether the

number of successful outcomes is greater than the unsuccessful and vice versa. If there are more

unsuccessful outcomes than successful, the counter outputs a line to the ‘unsuccessful locker’. When

using a D-Latch or D-Flip-Flop, the ‘D’ input must be turned on (1) for it to store this value and output

it. As shown in Figure 4, once the unsuccessful outcomes surpass the successful, the circuit is locked;

meaning no further alterations can be made. If we wanted this logic to be true, an implementation of

a NOT gate is needed before the ‘successful locker’ which blocks the value from passing through;

even if there is a maximum of 7 successful outcomes after the circuit is already locked. Furthermore,

the only case where the simulation stops as a result of the successful outcomes is if it reaches its

maximum of 7 successful accelerations. However, this does not lock the circuit, hence the use of the

NOT gate before the AND gate.

Page 1 of 9

1007ICT: Computer Systems and Networks

Logisim Assignment

Circuit Diagrams:

Figure 1 – 3-8 decoder:

Figure 2 – V0 to V7 selectors:

Page 2 of 9

1007ICT: Computer Systems and Networks

Logisim Assignment

[Show More]