Computer Architecture > Quiz > CSE490-590 Quiz 1 2025 Quiz 1 – V2| Answered 2025/2026. (All)

CSE490-590 Quiz 1 2025 Quiz 1 – V2| Answered 2025/2026.

Document Content and Description Below

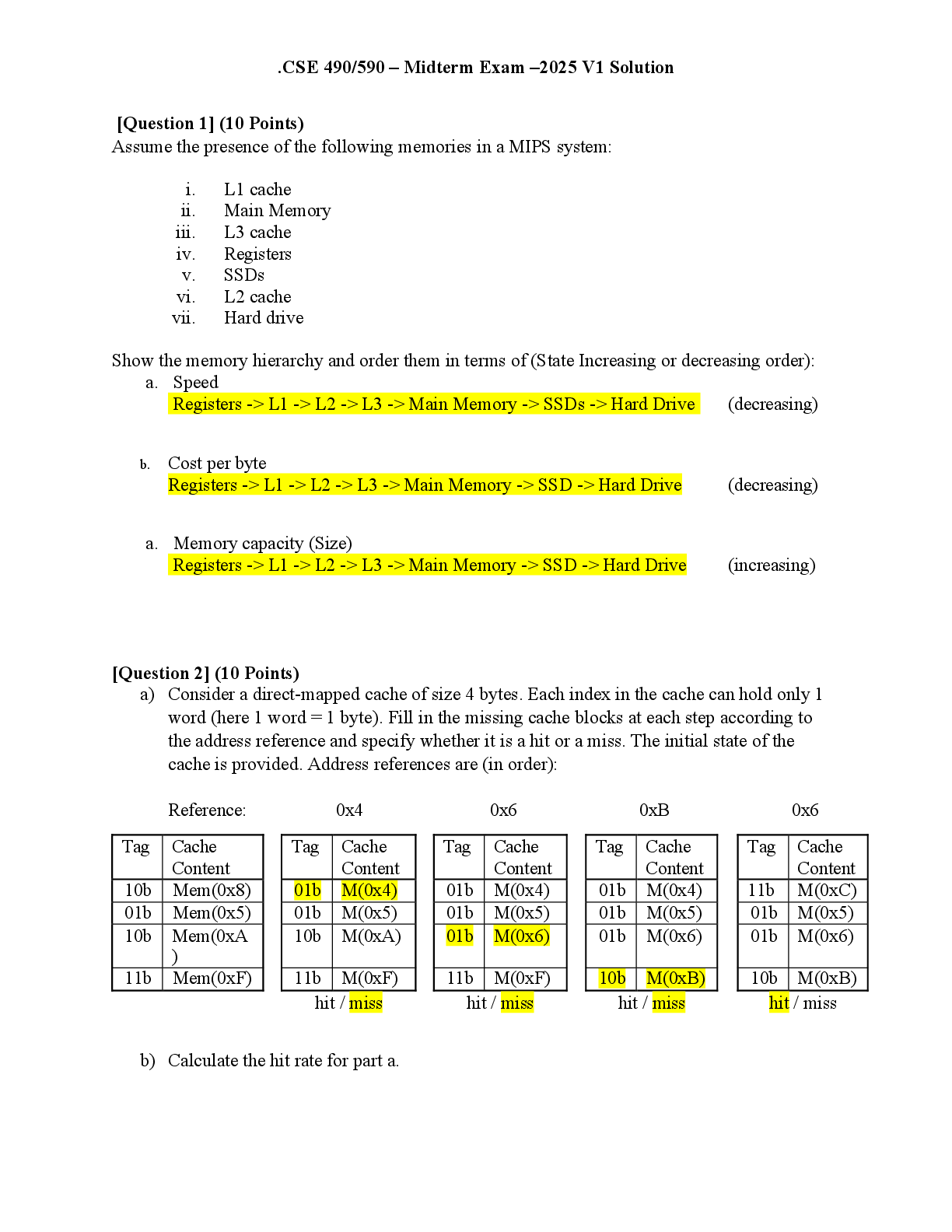

CSE490-590 Quiz 1 2025 Quiz 1 – V2 [Question 1] (6 Points) Suppose that we want to enhance the processor used for web serving. The new processor is 4 times faster on computation in a given web s... erving application than the original processor. Assuming that the original processor was busy with computation 60% of the time and was waiting for I/O 40% of the time, what is the overall speedup gained by incorporating the enhancement? Show your work. [Question 2] (6 Points) A program's run time for a given processor is determined using the number of instructions per program, the number of cycles per instruction, and clock frequency of the processer. Consider a program with the following instruction mix. Find the CPI for the same. Show your work. Instructions % cycle branch 20% 3 integer ALU 45% 1 load 20% 4 sw 15% 2 Updated [Question 3] (6 Points) Provide the binary representation for the following instruction: [Use Green Sheet attached] (Show your work) lw $s1,6($t1) [Question 4] [10 Points] a. Consider a byte-addressable memory system with the following contents: (3 points) Memory Location Value 0x1246 0x54 0x1247 0x16 0x1248 0x95 0x1249 0x55 0x124a 0x23 0x124b 0x17 0x124c 0x69 0x124d 0x85 If the following instruction is executed: lw $t1, 4($t0) $t0 contains the address 0x1244. What will $t1 contain? Use Big-Endian. b. Assume that $s0 contains the value 0x54545454 and $s1contains the address 0x12345B40. Assume that the memory data, starting from address 0x54545454 is: 0x79866608. What will be the value of $s0 after the following code is executed: Show your work. (7 points) (i) lh $s1, 0($s0) (ii) lb $s1, 1($s0) Updated [Question 5] (12 Points) Given the following single cycle MIPS datapath: a. For each of the following instructions, list the stages that are necessary for the execution of the given instruction: (IF, ID, EX, MEM, WB) i. add $t6, $s3, $s2 ii. b. For each of the following instructions, list the component numbers (as shown in the diagram above) that are required for the given instruction: i. add $t6, $s3, $s2 in red Page 5 ii. sw $s3, 24($s1) in green Updated [Question 6] (10 Points) Consider the following MIPS instruction sequence: add $s3, $s2, $s1 a. Find the data (RAW) hazards for the above instruction sequence and explain why it creates such hazard(s). (3 Points) Line 2 reads from $s3 while line 1 hasn't updated the value stored in the register yet, causing a RAW hazard. Line 4 and 5 read from $t0 while line 3 hasn't fetched the data from memory yet, causing a RAW hazard. b. Show the pipeline diagram after inserting Data Forwarding Unit to overcome data dependencies: (5 Points) (c) If you did not use forwarding to handle data hazards as in (b), how many more clock cycles it will take to complete the instruction sequence above. (2 points) Page 7 [Show More]

Last updated: 3 weeks ago

Preview 1 out of 6 pages

Buy this document to get the full access instantly

Instant Download Access after purchase

Buy NowInstant download

We Accept:

Reviews( 0 )

$10.50

Can't find what you want? Try our AI powered Search

Document information

Connected school, study & course

About the document

Uploaded On

Jul 11, 2025

Number of pages

6

Written in

Additional information

This document has been written for:

Uploaded

Jul 11, 2025

Downloads

0

Views

15