Computer Science > QUESTIONS & ANSWERS > 2020Fa18_HW6_soln Georgia Institute Of Technology ECE 2020 (All)

2020Fa18_HW6_soln Georgia Institute Of Technology ECE 2020

Document Content and Description Below

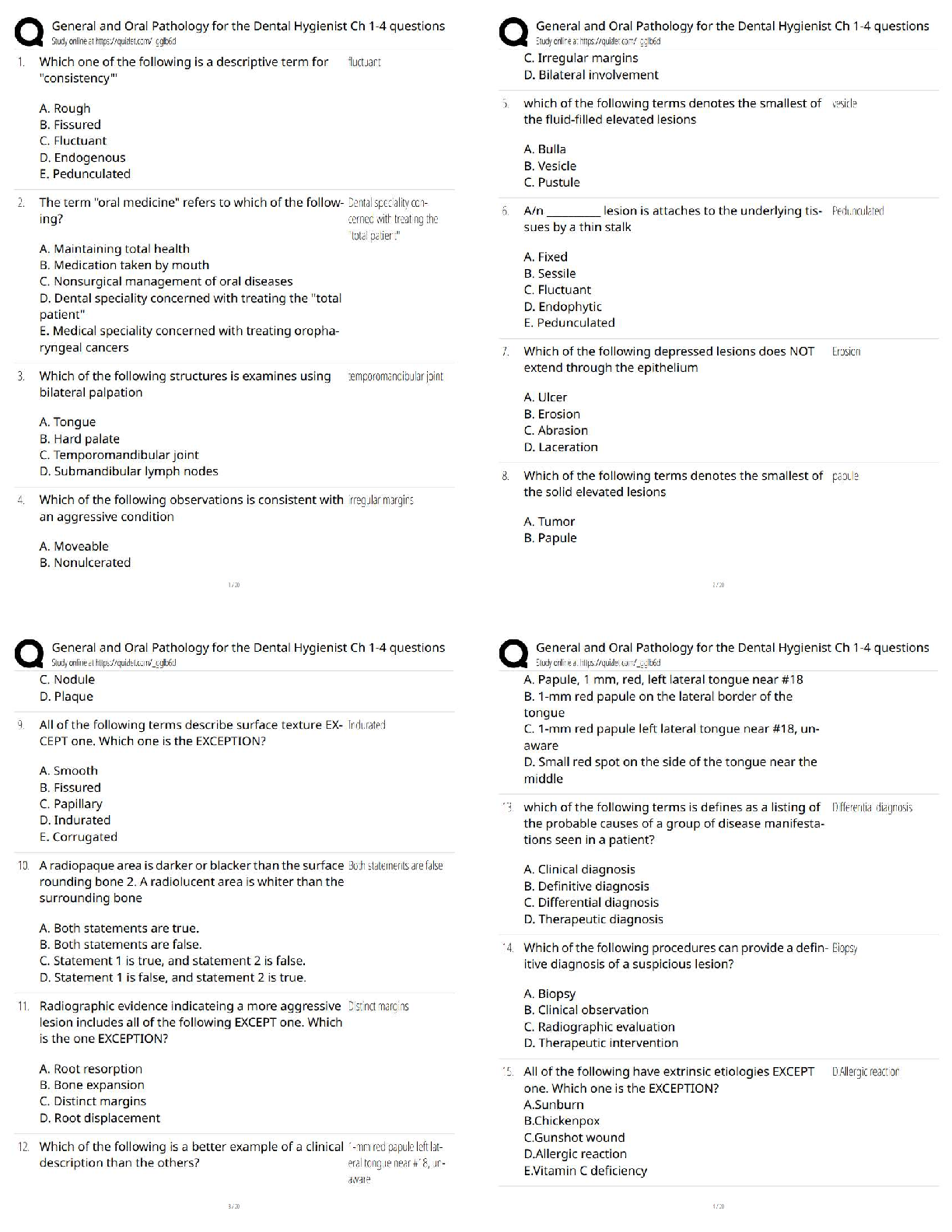

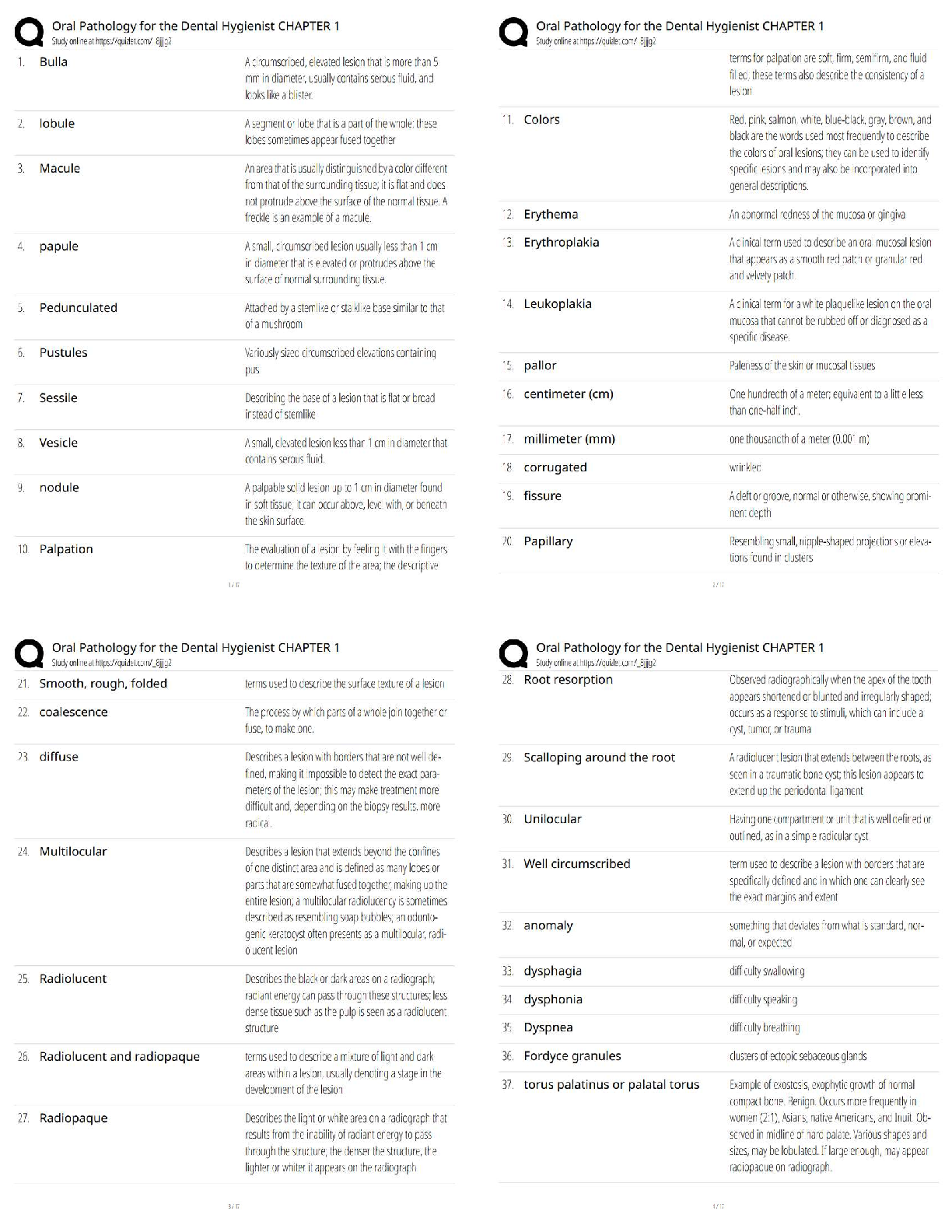

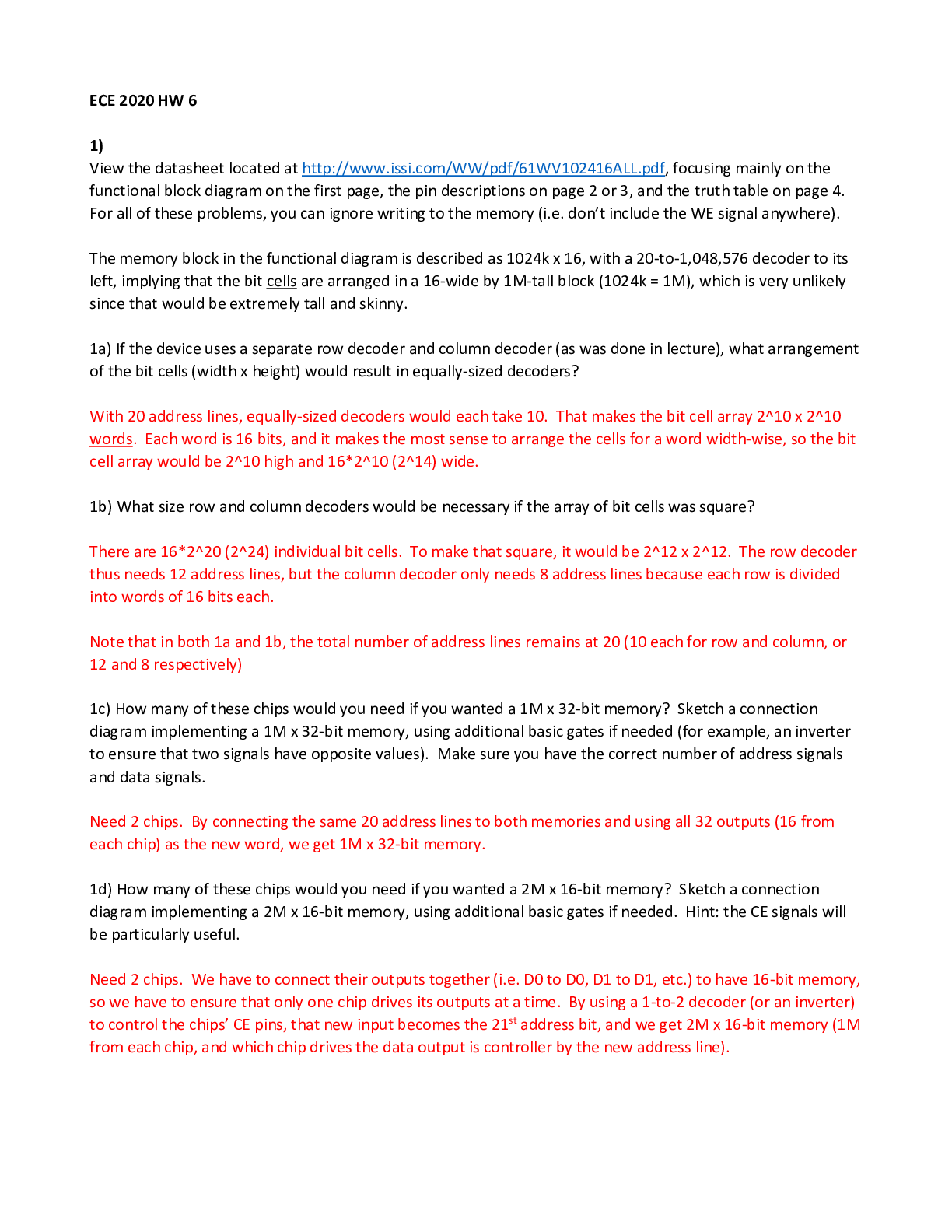

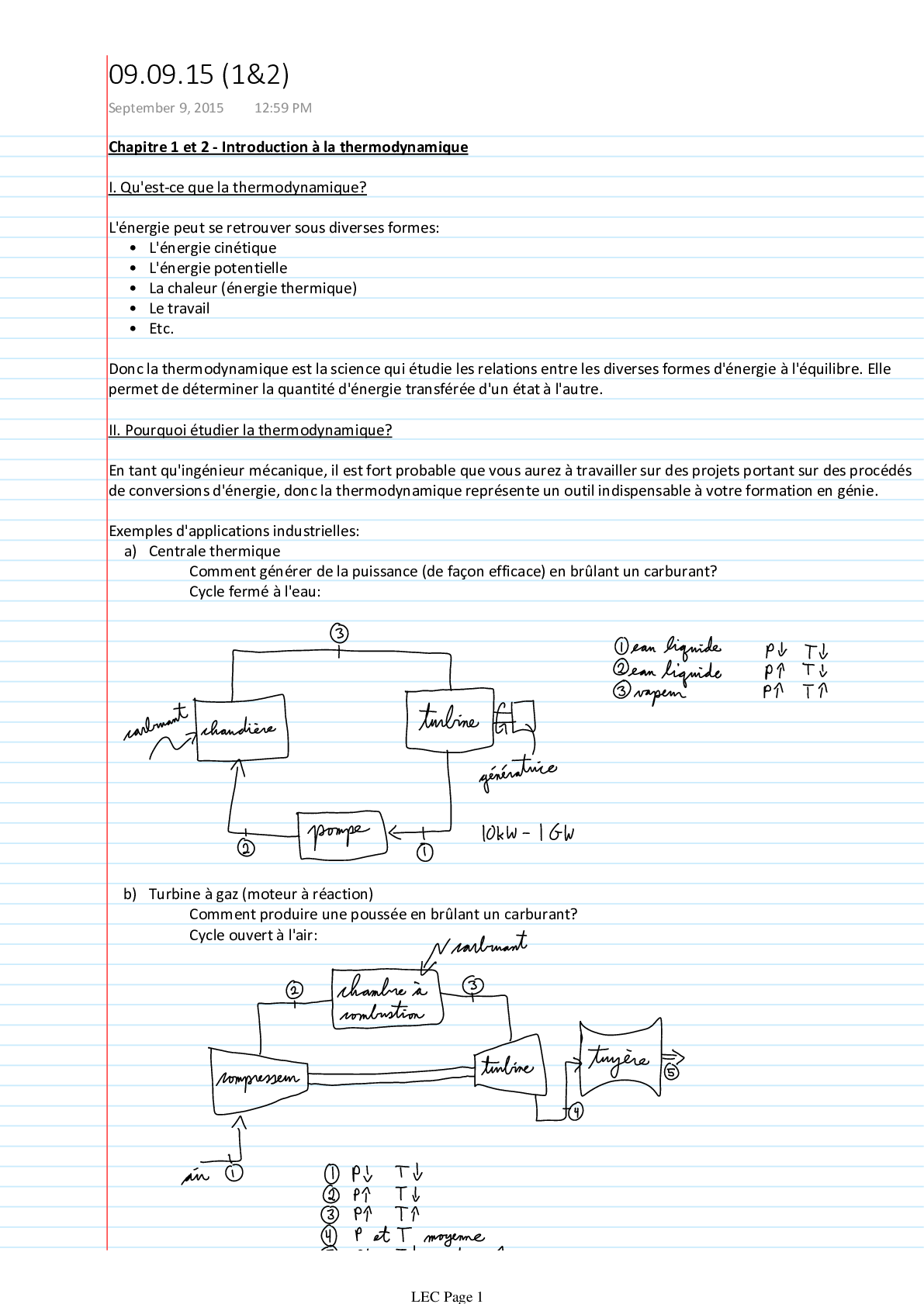

ECE 2020 HW 6 1) View the datasheet located at http://www.issi.com/WW/pdf/61WV102416ALL.pdf, focusing mainly on the functional block diagram on the first page, the pin descriptions on page 2 or 3, ... and the truth table on page 4. For all of these problems, you can ignore writing to the memory (i.e. don’t include the WE signal anywhere). The memory block in the functional diagram is described as 1024k x 16, with a 20-to-1,048,576 decoder to its left, implying that the bit cells are arranged in a 16-wide by 1M-tall block (1024k = 1M), which is very unlikely since that would be extremely tall and skinny. 1a) If the device uses a separate row decoder and column decoder (as was done in lecture), what arrangement of the bit cells (width x height) would result in equally-sized decoders? With 20 address lines, equally-sized decoders would each take 10. That makes the bit cell array 2^10 x 2^10 words. Each word is 16 bits, and it makes the most sense to arrange the cells for a word width-wise, so the bit cell array would be 2^10 high and 16*2^10 (2^14) wide. 1b) What size row and column decoders would be necessary if the array of bit cells was square? There are 16*2^20 (2^24) individual bit cells. To make that square, it would be 2^12 x 2^12. The row decoder thus needs 12 address lines, but the column decoder only needs 8 address lines because each row is divided into words of 16 bits each. Note that in both 1a and 1b, the total number of address lines remains at 20 (10 each for row and column, or 12 and 8 respectively) 1c) How many of these chips would you need if you wanted a 1M x 32-bit memory? Sketch a connection diagram implementing a 1M x 32-bit memory, using additional basic gates if needed (for example, an inverter to ensure that two signals have opposite values). Make sure you have the correct number of address signals and data signals. Need 2 chips. By connecting the same 20 address lines to both memories and using all 32 outputs (16 from each chip) as the new word, we get 1M x 32-bit memory. 1d) How many of these chips would you need if you wanted a 2M x 16-bit memory? Sketch a connection diagram implementing a 2M x 16-bit memory, using additional basic gates if needed. Hint: the CE signals will be particularly useful. Need 2 chips. We have to connect their outputs together (i.e. D0 to D0, D1 to D1, etc.) to have 16-bit memory, so we have to ensure that only one chip drives its outputs at a time. By using a 1-to-2 decoder (or an inverter) to control the chips’ CE pins, that new input becomes the 21st address bit, and we get 2M x 16-bit memory (1M from each chip, and which [Show More]

Last updated: 3 years ago

Preview 1 out of 2 pages

Buy this document to get the full access instantly

Instant Download Access after purchase

Buy NowInstant download

We Accept:

Reviews( 0 )

$4.00

Can't find what you want? Try our AI powered Search

Document information

Connected school, study & course

About the document

Uploaded On

Dec 04, 2022

Number of pages

2

Written in

All

Additional information

This document has been written for:

Uploaded

Dec 04, 2022

Downloads

0

Views

108

.png)

.png)